FPGA/LSI設計受託サービス

- ホーム

- FPGA/LSI設計受託サービス

ハードウェア・ソフトウェアの両側面から最適なFPGA/ASIC設計をご提案します。

また、既にディスコンになったデバイスのEOL対応も行います。

FPGA/LSI受託サービスの流れ

- 要求仕様分析

- 詳細仕様検討

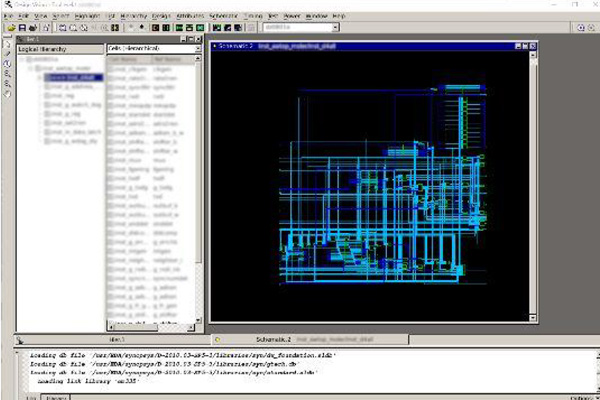

- 論理設計

- 制約ファイルの作成

- 論理合成

- タイミング検証

-

FPGA:書き込み

ASIC:ASICベンダーレイアウト・試作 - 実機検証

EOL対応(生産中止・ディスコン)

FPGA/LSIのEOL(生産中止・ディスコン)に伴う

設計変更・検証業務全般をサポートいたします。

複数のデバイスを1つの最適なFPGA/LSIにまとめるお手伝いをします。

回路図しか残っていない場合も、解読してRTLに置き換え可能です。

また、非同期回路を同期回路に置き換えます。

そして、新たにシミュレーション検証パターンを作成して論理検証を行い、実機上にて互換性を検証します。

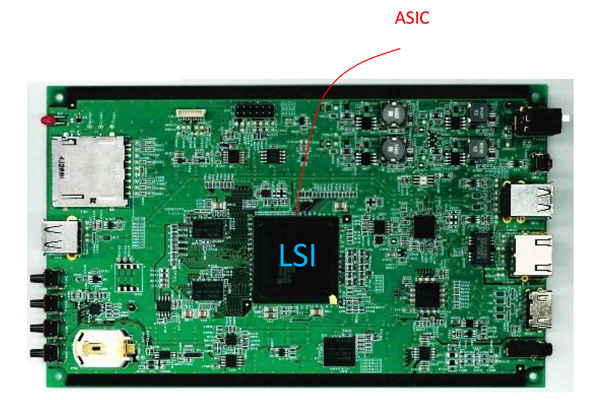

LSIのEOLに伴う置き換え事例

-

01現行LSI(GA)→ EOL決定

-

- 回路図ベースでの設計(大部分が非同期回路)

-

- 現行LSI仕様書

- 量産中製品基板

-

-

02仕様書、回路図からRTL作成(同期回路)

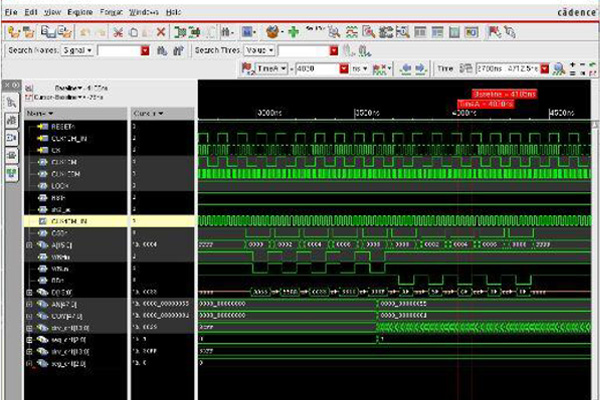

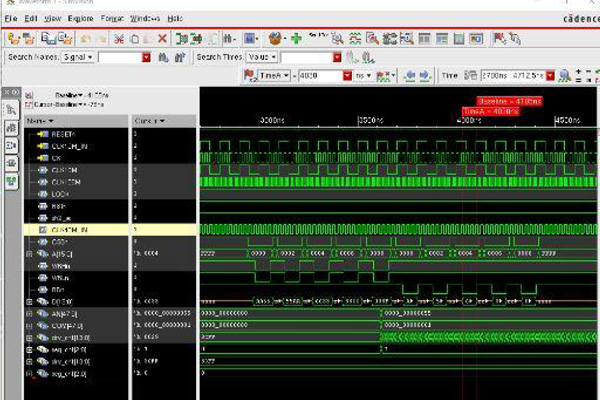

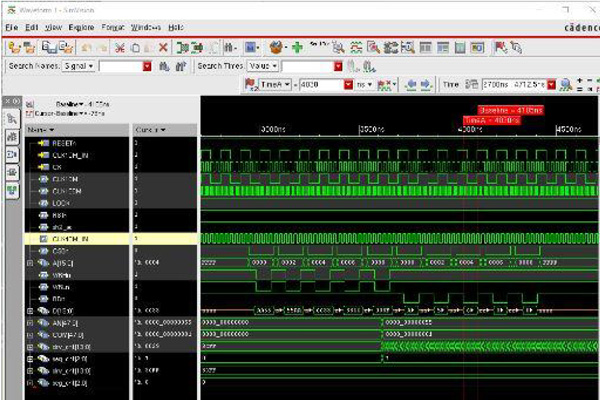

- RTL検証(nc-simによるシミュレーション)

-

03FPGA作成

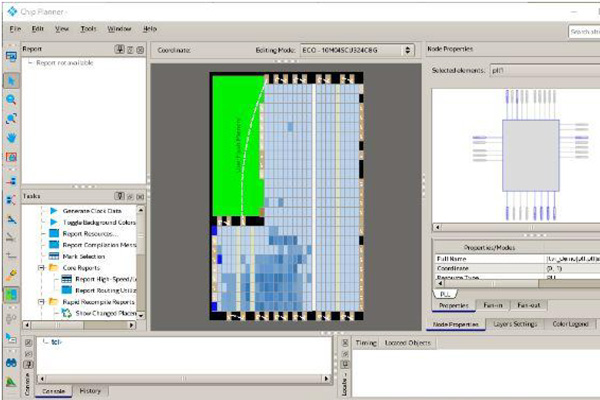

- ピン配置作成

- SDC作成

- 論理合成

- レイアウト

- STAによるタイミング確認

-

04FPGA評価

- FPGA用基板作成

- 実機評価

-

05LSI(ASIC)フロントエンド設計(ピン互換)

- IOセル/マイクロセルをLSI用に置き換え

- DFT設計(SCAN対応)

- RTL検証(nc-simによるシミュレーション)

- SDC作成

- 消費電力見積り(パッケージ見積り)

-

06LSI(ASIC)バックエンド設計(LSIベンダーでの作業)

- 論理合成

- レイアウト

- フォーマリティ

- デザインルールチェック(DRC)

- STA

- 故障検出率

-

07LSI(ASIC)レイアウト後検証

- フォーマリティ結果確認

- デザインルールチェック結果確認

- STA結果確認

- 故障検出率結果確認

- ネットリスト+SDCでの実遅延シミュレーション

-

08LSI(ASIC)量産(EOL対応完了)

- 現行基板での量産継続

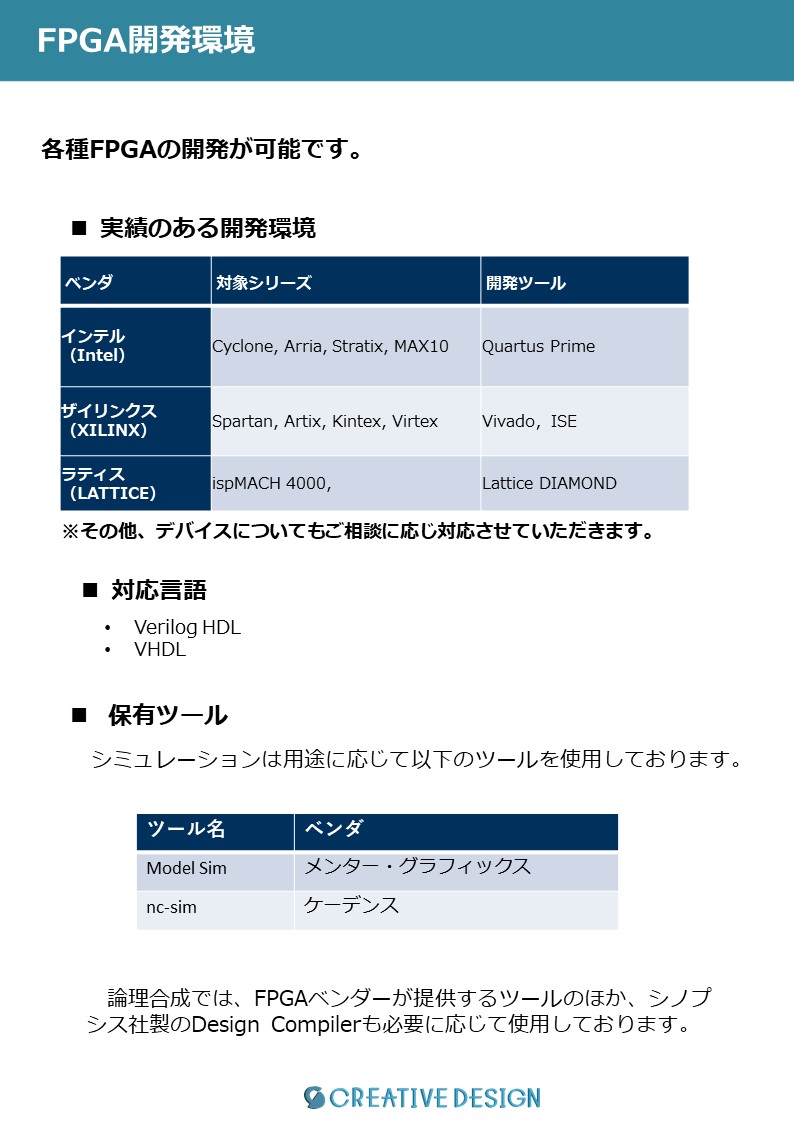

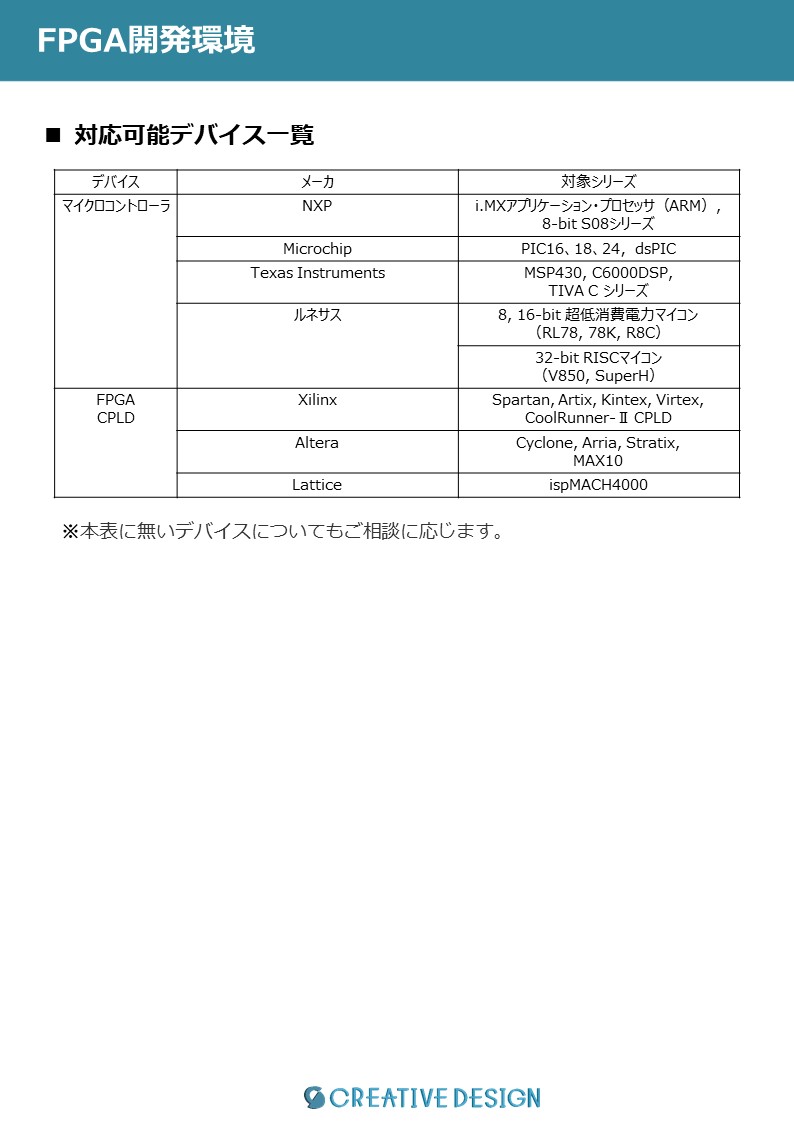

FPGA開発環境

各種FPGA開発が可能です。

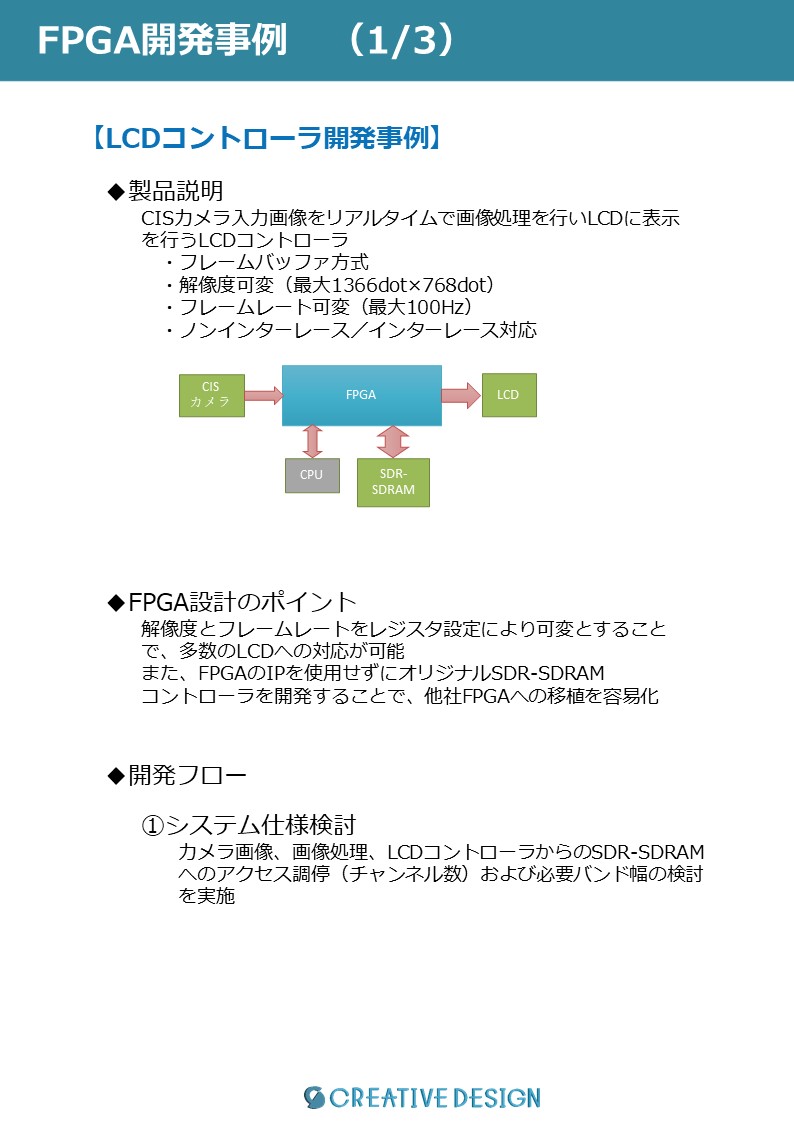

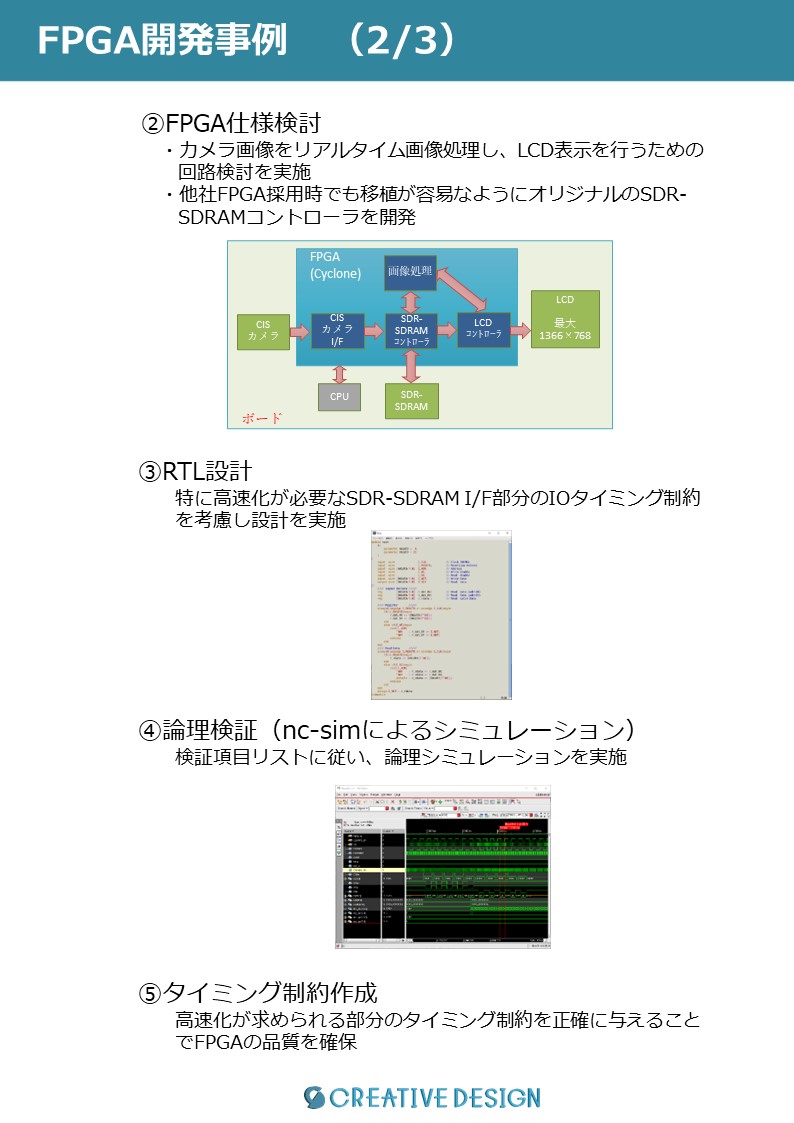

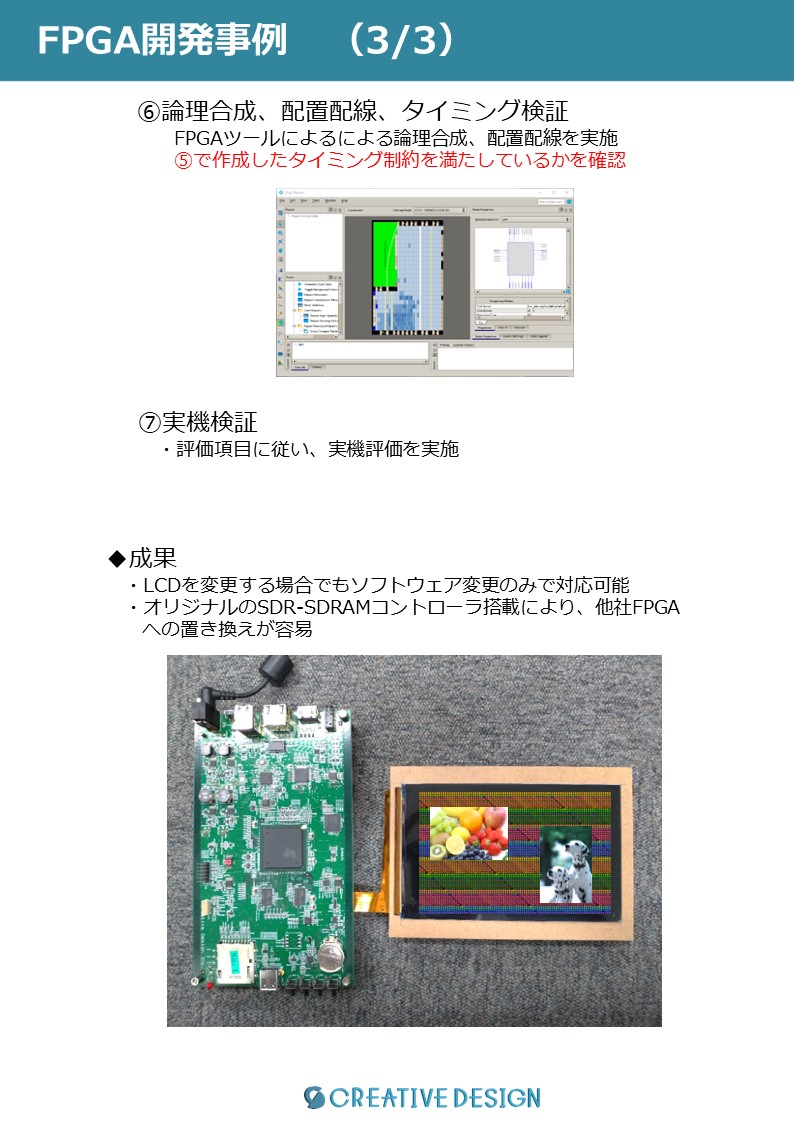

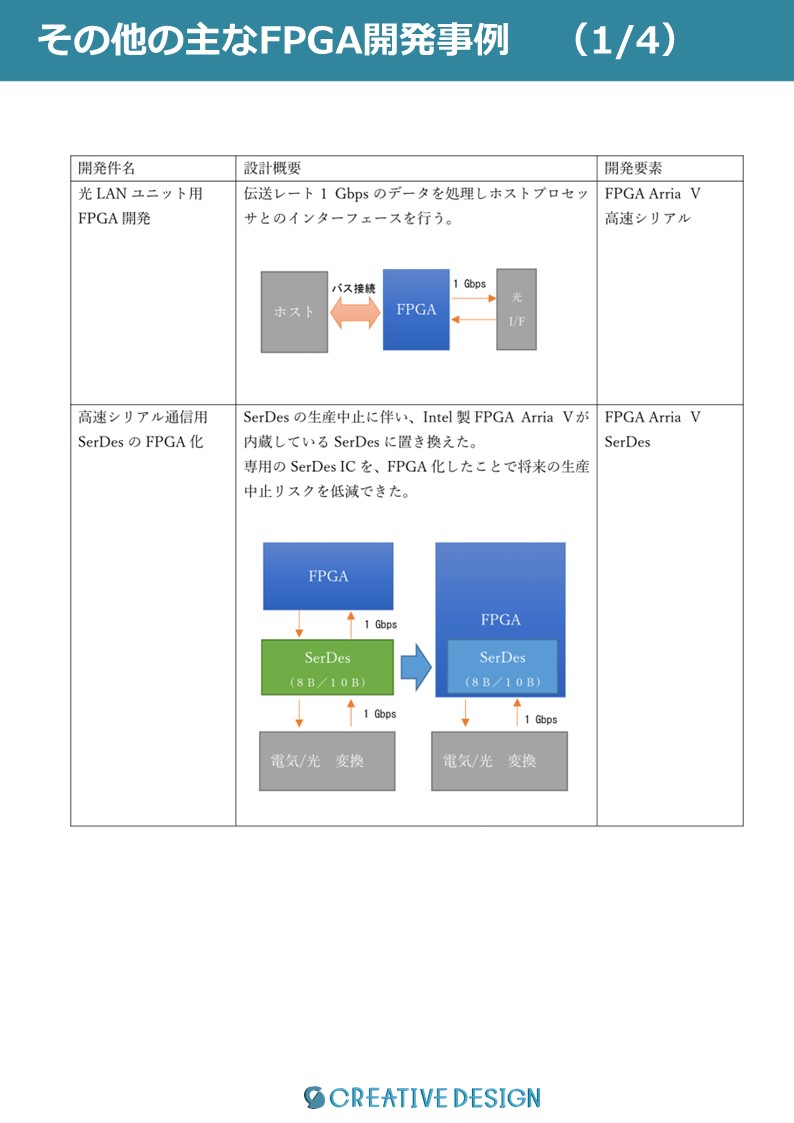

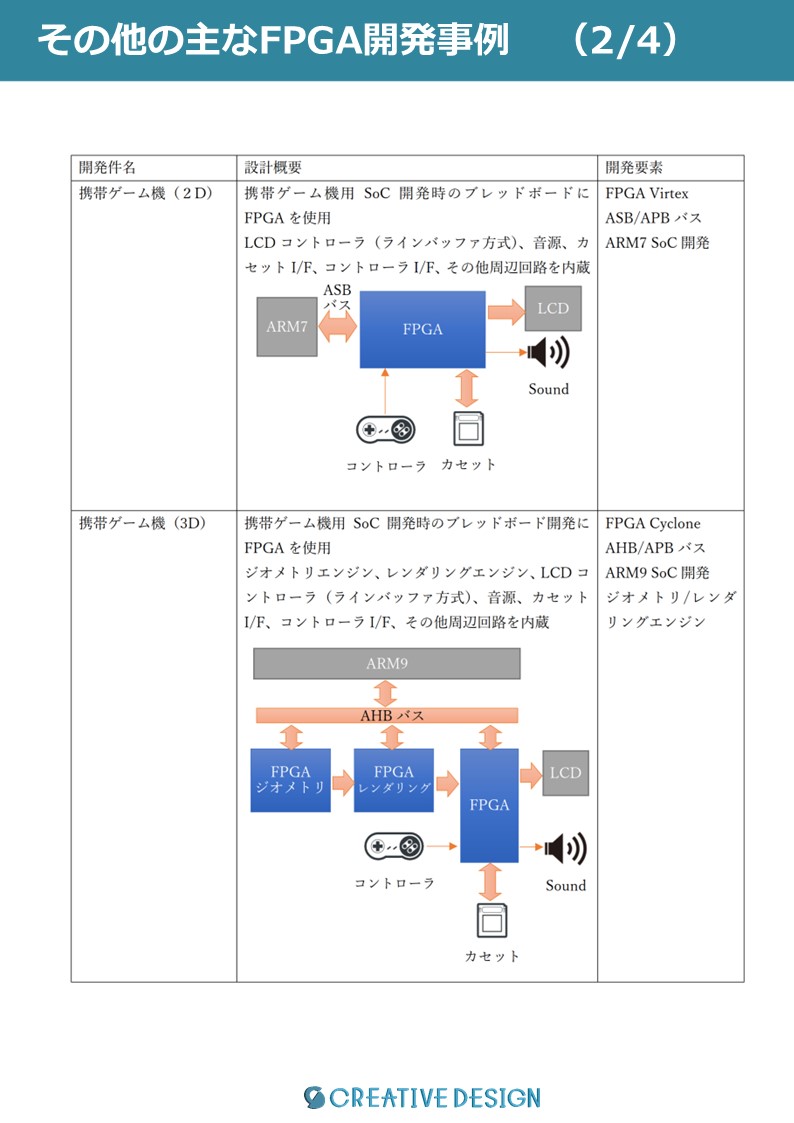

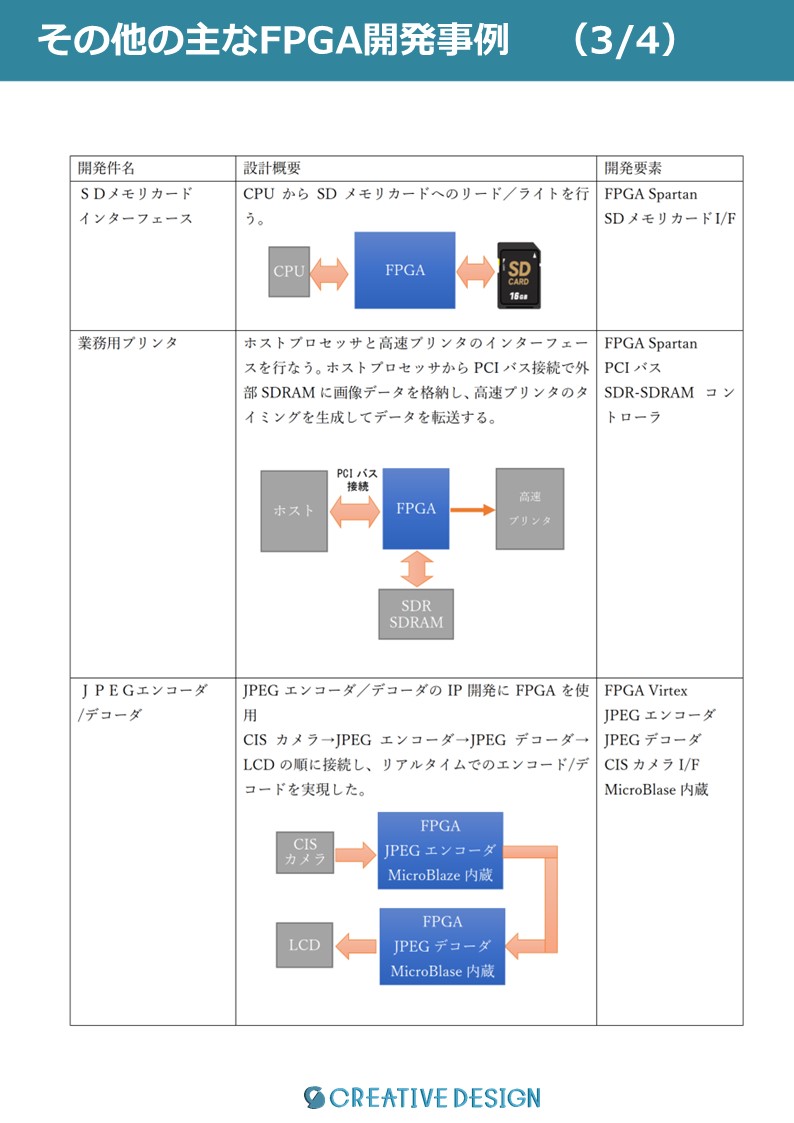

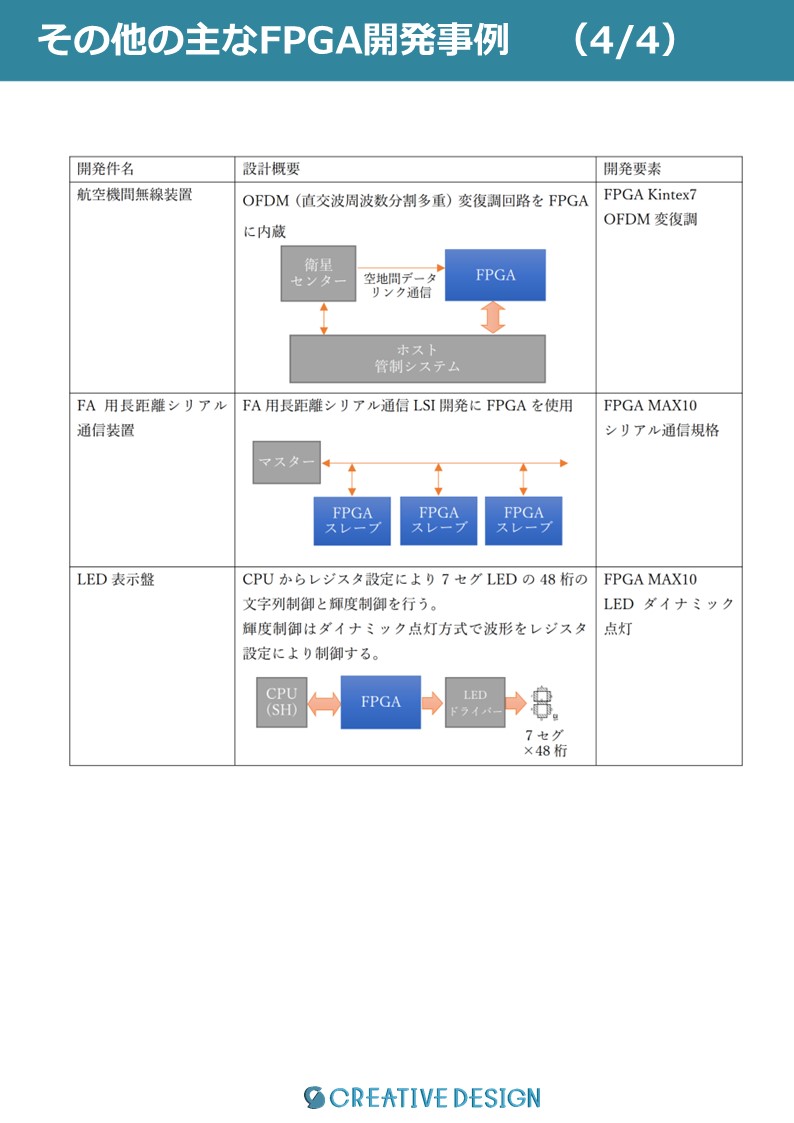

FPGA開発事例

その他の開発事例

お問合わせCONTACT

ご質問・ご相談などございましたら、

お気軽にお問合わせくださいませ。