# FPGA/ASIC 設計受託サービス

ハードウェア・ソフトウェアの両側面から 最適なFPGA/ASIC設計をご提案します。

株式会社クリエイティブ・デザイン

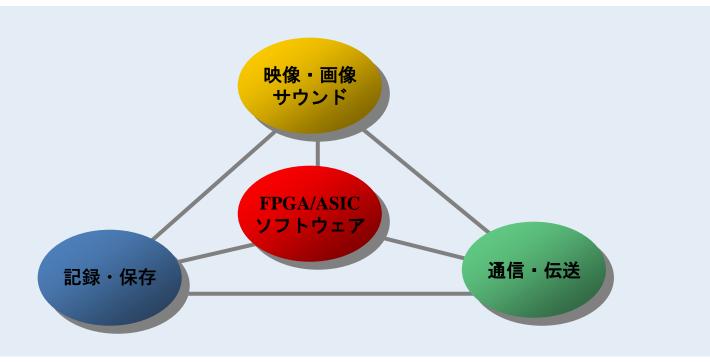

#### 3分野の要素技術をサポート

音声・画像、記録・保存、通信・伝送の製品開発でニーズの多い要素技術を、 FPGA/ASICとソフトウェアでサポートします。

### トータルソリューションでサポート

お客様の新製品開発のニーズに対して、

- ・企画提案、最適なソリューションの提案

- · FPGA/ASIC 論理設計

- ・論理検証・タイミング検証

- ・ソフトウェア開発

- ・システム(ボード)設計・試作

- ・機構、外装の試作

のトータルソリューションでお応えします。

### FPGA/ASIC設計受託サービス

#### 【お客様の製品に最適なFPGA/ASIC設計をご提案】

- ハード・ソフトの両側面から最適なFPGA/ASIC設計をご提案します。

- EOL対応で、紙の回路図しか残っていない場合や 論理検証用のパ ターンが無い場合もFPGA/ASIC化をサポートします。

- **論理検証だけでなく、実機検証も行うことで品質を確保します。**

#### FPGA/ASIC開発フロー

✓ 各ステップでお客様と共同レビュー を実施します。

### FPGA開発環境

#### 各種FPGAの開発が可能です。

#### ■ 実績のある開発環境

| ベンダ                | 対象シリーズ                         | 開発ツール           |

|--------------------|--------------------------------|-----------------|

| インテル<br>(Intel)    | Cyclone, Arria, Stratix, MAX10 | Quartus Prime   |

| ザイリンクス<br>(XILINX) | Spartan, Artix, Kintex, Virtex | Vivado, ISE     |

| ラティス<br>(LATTICE)  | ispMACH 4000,                  | Lattice DIAMOND |

※その他、デバイスについてもご相談に応じ対応させていただきます。

#### ■ 対応言語

- Verilog HDL

- VHDL

#### ■ 保有ツール

シミュレーションは用途に応じて以下のツールを使用しております。

| ツール名      | ベンダ          |

|-----------|--------------|

| Model Sim | メンター・グラフィックス |

| nc-sim    | ケーデンス        |

論理合成では、FPGAベンダーが提供するツールのほか、シノプシス社製のDesign Compilerも必要に応じて使用しております。

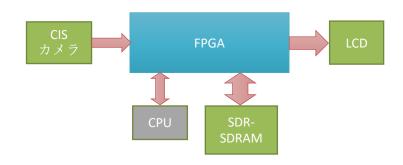

#### 【LCDコントローラ開発事例】

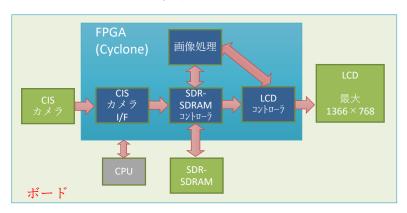

#### ◆製品説明

CISカメラ入力画像をリアルタイムで画像処理を行いLCDに表示を行うLCDコントローラ

- ・フレームバッファ方式

- ・解像度可変(最大1366dot×768dot)

- ・フレームレート可変(最大100Hz)

- ・ ノンインターレース/インターレース対応

#### ◆FPGA設計のポイント

解像度とフレームレートをレジスタ設定により可変とすることで、多数のLCDへの対応が可能 また、FPGAのIPを使用せずにオリジナルSDR-SDRAM コントローラを開発することで、他社FPGAへの移植を容易化

#### ◆開発フロー

#### ①システム仕様検討

カメラ画像、画像処理、LCDコントローラからのSDR-SDRAMへのアクセス調停(チャンネル数)および必要バンド幅の検討を実施

#### ②FPGA仕様検討

- ・カメラ画像をリアルタイム画像処理し、LCD表示を行うための 回路検討を実施

- ・他社FPGA採用時でも移植が容易なようにオリジナルのSDR-SDRAMコントローラを開発

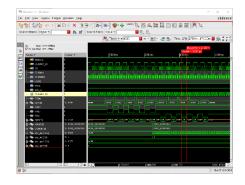

#### ③RTL設計

特に高速化が必要なSDR-SDRAM I/F部分のIOタイミング制約を考慮し設計を実施

④論理検証(nc-simによるシミュレーション) 検証項目リストに従い、論理シミュレーションを実施

#### ⑤タイミング制約作成

高速化が求められる部分のタイミング制約を正確に与えることでFPGAの品質を確保

### FPGA開発事例 (3/3)

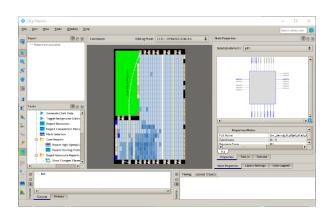

# ⑥論理合成、配置配線、タイミング検証 FPGAツールによるによる論理合成、配置配線を実施 ⑤で作成したタイミング制約を満たしているかを確認

#### ⑦実機検証

・評価項目に従い、実機評価を実施

#### ◆成果

- ・LCDを変更する場合でもソフトウェア変更のみで対応可能

- ・オリジナルのSDR-SDRAMコントローラ搭載により、他社FPGA への置き換えが容易

## その他の主なFPGA開発事例 (1/4)

| 開発件名            | 設計概要                                  | 開発要素         |

|-----------------|---------------------------------------|--------------|

| 光 LAN ユニット用     | 伝送レート1 Gbps のデータを処理しホストプロセッ           | FPGA Arria V |

| FPGA 開発         | サとのインターフェースを行う。                       | 高速シリアル       |

|                 | バス接続<br>FPGA 1 Gbps 光<br>I/F          |              |

| <br>  高速シリアル通信用 | SerDes の生産中止に伴い、Intel 製 FPGA Arria Vが | FPGA Arria V |

| SerDes の FPGA 化 | 内蔵している SerDes に置き換えた。                 | SerDes       |

|                 | <br> 専用の SerDes IC を、FPGA 化したことで将来の生産 |              |

|                 | 中止リスクを低減できた。                          |              |

|                 |                                       |              |

|                 | FPGA                                  |              |

|                 | 1 Gbps FPGA                           |              |

|                 | SerDes SerDes                         |              |

|                 | (8 B/1 0 B) (8 B/1 0 B)               |              |

|                 | 1 Gbps                                |              |

|                 | 電気/光 変換 電気/光 変換                       |              |

|                 |                                       |              |

## その他の主なFPGA開発事例 (2/4)

| 開発件名       | 設計概要                                                            | 開発要素                      |

|------------|-----------------------------------------------------------------|---------------------------|

| 携帯ゲーム機(2D) | 携帯ゲーム機用 SoC 開発時のブレッドボードに                                        | FPGA Virtex               |

|            | FPGA を使用                                                        | ASB/APB バス                |

|            | LCD コントローラ(ラインバッファ方式)、音源、カ                                      | ARM7 SoC 開発               |

|            | セット I/F、コントローラ I/F、その他周辺回路を内蔵                                   |                           |

|            | ASB  FPGA  LCD  Sound  Sound                                    |                           |

| 携帯ゲーム機(3D) | 携帯ゲーム機用 SoC 開発時のブレッドボード開発に<br>FPGA を使用                          | FPGA Cyclone              |

|            | デFGA を使用<br>ジオメトリエンジン、レンダリングエンジン、LCD コ                          | AHB/APB バス<br>ARM9 SoC 開発 |

|            | ントローラ (ラインバッファ方式)、音源、カセット                                       |                           |

|            | I/F、コントローラ I/F、その他周辺回路を内蔵                                       | リングエンジン                   |

|            | ARM9  AHBバス  FPGA ジオメトリ  FPGA レンダリング  FPGA  コントローラ  Sound  カセット |                           |

## その他の主なFPGA開発事例 (3

# (3/4)

| BB 3W M. F | anal limae                                                  | HI W. T. +          |

|------------|-------------------------------------------------------------|---------------------|

| 開発件名       | 設計概要                                                        | 開発要素                |

| SDメモリカード   | CPU から SD メモリカードへのリード/ライトを行                                 | FPGA Spartan        |

| インターフェース   | う。<br>                                                      | SDメモリカードI/F         |

|            | CPU FPGA FPGA 1608                                          |                     |

| 業務用プリンタ    | ホストプロセッサと高速プリンタのインターフェー                                     | FPGA Spartan        |

|            | スを行なう。ホストプロセッサから PCI バス接続で外                                 | PCIバス               |

|            | <br>  部 SDRAM に画像データを格納し、高速プリンタのタ                           | SDR-SDRAM ¬>        |

|            | イミングを生成してデータを転送する。                                          | トローラ                |

|            |                                                             |                     |

|            | PCI バス<br>接続<br>アリンタ                                        |                     |

| JPEGエンコーダ  | JPEG エンコーダ/デコーダの IP 開発に FPGA を使                             | FPGA Virtex         |

| /デコーダ      | 用                                                           | JPEG エンコーダ          |

|            | CIS カメラ→JPEG エンコーダ→JPEG デコーダ→                               | JPEG デコーダ           |

|            | LCD の順に接続し、リアルタイムでのエンコード/デ                                  | CIS カメラ I/F         |

|            | コードを実現した。                                                   | <br>  MicroBlase 内蔵 |

|            | FPGA JPEG エンコーダ MicroBlaze 内蔵  FPGA JPEG デコーダ MicroBlase 内蔵 |                     |

# その他の主なFPGA開発事例 (4/4)

| 開発件名                | 設計概要                                                                                                                                                | 開発要素                           |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 航空機間無線装置            | OFDM (直交波周波数分割多重) 変復調回路を FPGA         に内蔵         第星         センター         空地間データ<br>リンク通信         ホスト<br>管制システム                                     | FPGA Kintex7<br>OFDM 変復調       |

| FA 用長距離シリアル<br>通信装置 | FA 用長距離シリアル通信 LSI 開発に FPGA を使用  マスター  FPGA FPGA スレーブ  スレーブ  スレーブ                                                                                    | FPGA MAX10<br>シリアル通信規格         |

| LED 表示盤             | CPU からレジスタ設定により 7 セグ LED の 48 桁の 文字列制御と輝度制御を行う。         輝度制御はダイナミック点灯方式で波形をレジスタ 設定により制御する。         CPU (SH)         FPGA         LED ドライバー スタ メ48 桁 | FPGA MAX10<br>LED ダイナミック<br>点灯 |

### お問い合わせ先

【名称】株式会社クリエイティブ・デザイン

【住所】〒666-0024 兵庫県川西市久代3丁目13番21号

**TEL** 072-757-2725

[URL] <a href="http://www.cdi.co.jp/index.html">http://www.cdi.co.jp/index.html</a>

[E-mail] <a href="mailto:support@cdi.co.jp">support@cdi.co.jp</a>

2020/06/09